Der globale Wettlauf um die Hardware-Basis für künstliche Intelligenz erreicht einen neuen Siedepunkt. Während High Bandwidth Memory (HBM) jahrelang als das Nonplusultra für KI-Beschleuniger galt, zeichnet sich nun ein fundamentaler Wandel ab. Mit SOCAMM2 betritt ein neuer Speicherstandard die Bühne, der das Kräfteverhältnis im Rechenzentrum neu definieren könnte. Brancheninsidern zufolge bereiten sich die Chip-Giganten AMD und Qualcomm darauf vor, SOCAMM2 ab Anfang 2026 in ihre kommenden KI-Produktlinien zu integrieren. Dieser Schritt markiert eine strategische Abkehr von bisherigen Architekturen und zielt darauf ab, Speicherkapazität, Energieeffizienz und die Wirtschaftlichkeit von KI-Infrastrukturen massiv zu verbessern.

Der Flaschenhals der KI: Speicher wird zur Priorität

Lange Zeit stand die reine Rechenleistung von KI-Chips im Rampenlicht. Doch unserer Analyse nach verschiebt sich der kritische Hardware-Engpass rasant: Weg von den reinen FLOPs (Floating Point Operations), hin zur Speicherkapazität und -anbindung. Die explosionsartige Verbreitung von Large Language Models (LLMs) und komplexen multimodalen Modellen (MMMs) erzeugt einen unersättlichen Hunger nach Speicher, der nicht nur groß, sondern auch extrem energieeffizient und skalierbar sein muss. Diese Modelle benötigen gigantische Datenmengen unmittelbar am Prozessor – nicht nur für das Training, sondern vor allem für die Inferenz, also den produktiven Betrieb der KI im Alltag.

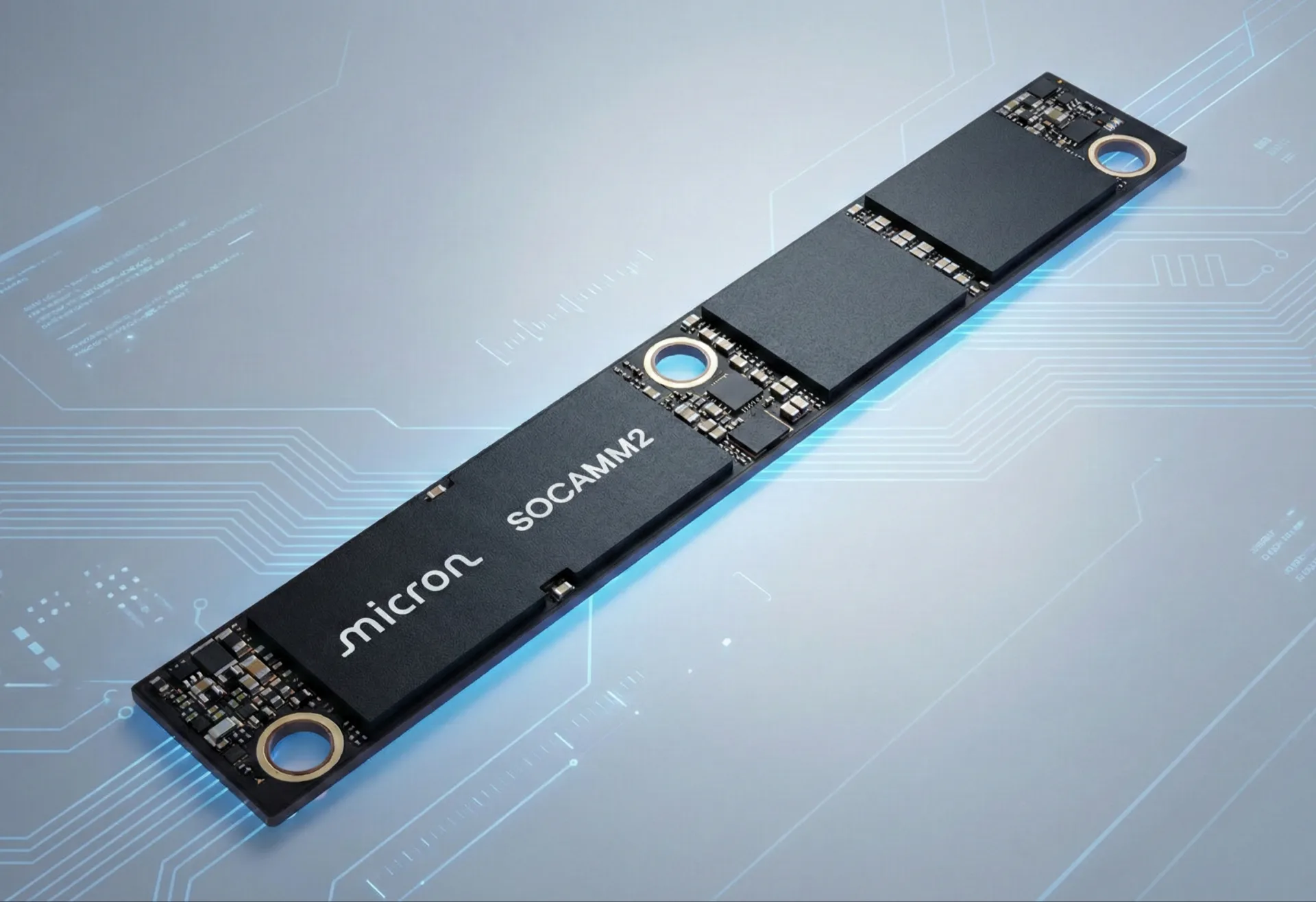

NVIDIA, mit einem Marktanteil von über 90 % bei KI-Chips, hat diesen Trend nicht dem Zufall überlassen. Das Unternehmen hat das Konzept des "System-on-Chip Advanced Memory Module" (SOCAMM) maßgeblich vorangetrieben und setzt bei seinen "Vera Rubin"-Beschleunigern auf den SOCAMM2-Standard. Nachdem die erste Generation (SOCAMM1) Berichten zufolge mit technischen Hürden zu kämpfen hatte, unterstreicht das Redesign auf SOCAMM2 die strategische Bedeutung dieses Standards. Nun ziehen AMD und Qualcomm nach. Dabei geht es nicht nur um die bloße Adaption eines Standards, sondern um individuelle Implementierungen, die eigene Wettbewerbsvorteile schaffen sollen.

SOCAMM2: Ein neuer „Active Workspace“ für die KI

Wir betrachten SOCAMM2 als ein entscheidendes evolutionäres Bindeglied. Es schließt die Lücke zwischen fest verlötetem LPDDR-Speicher (bekannt aus Smartphones) und den steckbaren, aber oft weniger effizienten Server-DIMMs. Strategisch zwischen dem extrem schnellen, aber kapazitätsbegrenzten HBM und dem herkömmlichen System-DRAM positioniert, etabliert SOCAMM2 einen sogenannten „Active Workspace“ – einen prozessornahen Speicherpool speziell für KI-Agenten.

Die Vorteile von SOCAMM2 im Überblick:

- Modular und flexibel: Im Gegensatz zu verlötetem Speicher sind SOCAMM2-Module austauschbar. Für Rechenzentren ist dies ein entscheidender Faktor für die Langlebigkeit der Plattformen, da Upgrades und Wartungen deutlich vereinfacht werden. Dies senkt die Total Cost of Ownership (TCO) erheblich.

- LPDDR-Technologie als Basis: SOCAMM2 nutzt die Energieeffizienz von LPDDR5X und dem kommenden LPDDR6. Insbesondere LPDDR6 verspricht mit einer projizierten Bandbreite von 38,4 GB/s pro Kanal bei gleichzeitig 20 % geringerem Stromverbrauch einen massiven Sprung für Hyperscale-KI-Anwendungen.

- Hohe Kapazität: Micron bemustert bereits Module mit 192 GB. In Systemen wie NVIDIAs GB300 NVL72 könnte SOCAMM2 auf LPDDR5X-Basis bis zu 18 TB Gesamtspeicher mit einer Systembandbreite von etwa 16 TB/s bereitstellen.

- Energieeffizienz: Da SOCAMM2 auf LPDDR basiert, verbraucht es weniger Strom als herkömmliche RDIMMs. Bei massiven KI-Clustern, in denen jeder Watt zählt, ist dies ein kritischer Wettbewerbsvorteil.

- Kompaktes Design: Die Bauweise vereinfacht das Routing auf der Platine und die Kühlung in hochdichten Rack-Systemen, die heute den Markt dominieren.

- JEDEC-Standard: Die Einhaltung des JEDEC-Standards (JESD328) garantiert Interoperabilität und Unabhängigkeit von einzelnen Herstellern, was eine gesunde Lieferkette fördert.

Im Kern erlaubt SOCAMM2 KI-Modellen, Millionen von Token und langlebige Zustände direkt im prozessornahen Speicherpool zu halten. Dies reduziert den Datenverkehr zwischen den Knoten und steigert die Effizienz. Auch wenn HBM schneller bleibt, überwiegen für viele Inferenz-Szenarien die Kapazitäts- und Kostenvorteile von SOCAMM2.

Qualcomms Angriff auf die Inferenz-Dominanz

Qualcomm, der Gigant für Mobilprozessoren, hat am 27. Oktober 2025 offiziell seinen Einstieg in den KI-Rechenzentrumsmarkt mit den Inferenz-Beschleunigern AI200 und AI250 angekündigt. Diese Chips, die 2026 (AI200) bzw. 2027 (AI250) auf den Markt kommen sollen, fordern NVIDIA und AMD direkt heraus – mit einem klaren Fokus auf LLM- und MMM-Inferenz.

Qualcomms Strategie basiert auf mehreren Säulen:

- Effizienz und TCO: Mit einer Leistungsaufnahme von 160 kW für ein flüssigkeitsgekühltes Rack-System setzt Qualcomm auf niedrige Betriebskosten. Die LPDDR-Basis von SOCAMM2 spielt hier eine zentrale Rolle.

- Massive LPDDR-Kapazität: Die AI200/AI250-Karten sind darauf ausgelegt, bis zu 768 GB LPDDR-Speicher pro Karte zu verwalten. Dies ist ideal für gigantische Kontextfenster moderner KI-Modelle. Qualcomm wirbt mit dem Versprechen: "Mehr Speicherkapazität für weniger Geld".

- Near-Memory Computing: Besonders der AI250 soll über eine Architektur verfügen, die Rechenleistung noch näher an den Speicher bringt. Qualcomm spricht von einer "effektiven Speicherbandbreite", die zehnmal höher als bei aktuellen NVIDIA-GPUs sein soll. Auch wenn solche Werbeversprechen mit Vorsicht zu genießen sind, zeigt die Richtung klar auf SOCAMM2 als "Active Workspace".

- Integration der Energieverwaltung (PMIC): Berichten zufolge entwickeln Qualcomm und AMD SOCAMM-Module, bei denen das Power Management (PMIC) direkt auf dem Modul sitzt. Diese quadratischen Module mit vier DRAM-Chips vereinfachen das Mainboard-Design und ermöglichen eine präzisere Spannungssteuerung, was bei den hohen Taktraten von LPDDR6 essenziell für die Signalintegrität ist.

Die Partnerschaft mit Humain aus Saudi-Arabien, die den Einsatz von Systemen mit bis zu 200 Megawatt ab 2026 vorsieht, belegt, dass Qualcomms Inferenz-fokussierter Ansatz bereits echtes Marktinteresse weckt.

AMDs strategische Position und der Schatten von OpenAI

Während AMDs Pläne für SOCAMM2 noch weniger detailliert bekannt sind als die von Qualcomm, deuten alle Zeichen auf eine Integration in die kommenden KI-Produktlinien hin. Strategisch ist dies für AMD zwingend erforderlich, um im direkten Vergleich mit NVIDIA nicht zurückzufallen. Die Kombination aus starken CPUs und GPUs für das Rechenzentrum mit der Kapazität und Effizienz von SOCAMM2 könnte AMD ein wichtiges Differenzierungsmerkmal verschaffen.

Besonders spannend ist die Rolle von OpenAI: Berichte, wonach OpenAI nicht nur Chips von AMD kaufen, sondern sich möglicherweise sogar an dem Unternehmen beteiligen möchte, könnten AMD massiven Rückenwind geben. Eine solche Allianz würde AMD helfen, die Dominanz von NVIDIA zu brechen und SOCAMM2 als neuen Standard in großem Stil zu etablieren.

Fazit: Ein Showdown im Rechenzentrum

Die breite Unterstützung für SOCAMM2 durch AMD und Qualcomm signalisiert eine branchenweite Bewegung hin zu optimierten Speicherlösungen. Angesichts eines prognostizierten Marktvolumens für KI-Server von 298 Milliarden Dollar bis 2025 steht extrem viel auf dem Spiel.

Trotz des Potenzials gibt es Hürden:

- Thermische Herausforderungen: Die hohe Packungsdichte von LPDDR-Chips auf kleinem Raum erfordert fortschrittliche Kühlkonzepte wie die direkte Flüssigkeitskühlung.

- LPDDR6-Entwicklung: Der Standard befindet sich noch in der Verifizierungsphase. Kosten und Stabilität bei Massenproduktion müssen sich erst noch beweisen.

- NVIDIAs Software-Vorsprung: Das größte Hindernis für AMD und Qualcomm bleibt NVIDIAs CUDA-Ökosystem, das eine enorme Bindungswirkung für Entwickler hat.

Dennoch: Die Dynamik hinter SOCAMM2 ist ungebrochen. Mit Schwergewichten wie Samsung, SK Hynix und Micron im Boot wird der Standard ab 2026/2027 die Hierarchie im Rechenzentrum umwälzen. Wir sind überzeugt, dass SOCAMM2 das Fundament für eine nachhaltigere und skalierbarere KI-Infrastruktur legt. Der Kampf um die Speicherherrschaft hat gerade erst begonnen.

Kommentare